# User Guide

# SC1-ALLEGRO • CompactPCI® Serial CPU Card Intel® Core™ i7-3xxx Processor Quad-Core (Ivy Bridge)

Document No. 6782 • Edition 30 • 4 October 2018

## Contents

| About this Manual        |                         | <br> | <br> | . 4 |

|--------------------------|-------------------------|------|------|-----|

| Edition History .        |                         | <br> | <br> | . 4 |

| Related Docume           | nts                     | <br> | <br> | . 5 |

| Nomenclature .           |                         | <br> | <br> | . 5 |

|                          |                         |      |      |     |

|                          | - Liability Exclusion . |      |      |     |

| 3                        |                         |      |      |     |

|                          |                         |      |      |     |

| Overview                 |                         | <br> | <br> | . / |

| Technical Features       |                         |      |      | 0   |

|                          |                         |      |      |     |

| •                        |                         |      |      |     |

|                          | tions                   |      |      |     |

| •                        | ents                    |      |      |     |

| 9                        |                         |      |      |     |

|                          | onent Assembly          |      |      |     |

|                          | nectors                 |      |      |     |

| Front Panel Swite        | ches & Indicators       | <br> | <br> | 13  |

| On-Board Conne           | ctors & Sockets         | <br> | <br> | 14  |

| Pin Headers              |                         | <br> | <br> | 14  |

| Jumpers                  |                         | <br> | <br> | 14  |

| •                        |                         |      |      |     |

| •                        | rations                 |      |      |     |

|                          |                         |      |      |     |

|                          | em                      |      |      |     |

|                          |                         |      |      |     |

|                          | ace (SATA)              |      |      |     |

|                          | erface                  |      |      |     |

|                          |                         |      |      |     |

|                          | Bus (USB)               |      |      |     |

|                          |                         |      |      |     |

|                          |                         |      |      |     |

|                          |                         |      |      |     |

|                          |                         |      |      |     |

| 3                        |                         |      |      |     |

|                          |                         |      |      |     |

|                          | r Good) LED             |      |      |     |

|                          | ral Purpose) LED        |      |      |     |

| HD (Hard                 | Disk Activity) LED      | <br> | <br> | 26  |

| EB (Etherr               | net Backplane) LED .    | <br> | <br> | 27  |

|                          | ply Control (PS_ON#     |      |      |     |

| Power Supply Sta         | atus (PWR_FAIL#)        | <br> | <br> | 27  |

| Mezzanine Side I         | Board Options           | <br> | <br> | 28  |

| _                        | rial                    |      |      |     |

|                          | ot Controller           |      |      |     |

|                          | Slot Operation          |      |      |     |

| •                        | t-Plug                  |      |      |     |

|                          |                         |      |      |     |

| Installing and Replacing | Components              | <br> | <br> | 42  |

|                          | 1                       |      |      |     |

|                          | ard                     |      |      |     |

|                          | pard                    |      |      |     |

| 3                        | dations                 |      |      |     |

| FINIC MECOIIIIIEII       | uuuloii3                | <br> | <br> | 40  |

# User Guide • SC1-ALLEGRO • CompactPCl® Serial CPU Board • Intel® i7-3xxx Processor

| nica           | al Reference                                |

|----------------|---------------------------------------------|

|                | ocal PCI Devices                            |

|                | ocal SMB Devices                            |

|                | Hardware Monitor LM87                       |

|                | Board Control and Status Registers          |

|                | Write/Read Control Register 0               |

|                |                                             |

|                | Read/Clear Status Register 1                |

|                | Read/Clear Status Register 1                |

| _              | Read PLD Revision Register                  |

| (              | GPIO Usage                                  |

|                | GPIO Usage QM77 PCH                         |

| (              | Configuration Jumpers                       |

|                | Configuration PCI Express Switch (DS-P)     |

|                | Loading UEFI BIOS Setup Defaults (P-GP)     |

|                | Manufacturer Mode Jumper (P-MFG)            |

|                | RTC Reset (P-RTC)                           |

| $\overline{C}$ | Connectors                                  |

|                | Front Panel Connectors                      |

|                | DisplayPort Connectors                      |

|                | VGA Video Connector                         |

|                | USB Connectors                              |

|                | Ethernet Connectors                         |

|                | Mezzanine Connectors                        |

|                | Expansion Interface J-EXP                   |

|                | High Speed Expansion Connector J-HSE        |

|                | PCI Express® Expansion Header J-PCIE        |

|                | SDVO/DisplayPort Expansion Header J-SDVO    |

|                | Pin Headers & Debug                         |

|                | Front Panel Handle Microswitch Header P-FPH |

|                | PLD Programming Header P-ISP                |

|                | Processor Debug Header XDP1                 |

|                | Backplane Connectors                        |

|                | CompactPCl® Serial Backplane Connector P1   |

|                | CompactPCI® Serial Backplane Connector P2   |

|                |                                             |

|                | CompactPCl® Serial Backplane Connector P3   |

|                | CompactPCl® Serial Backplane Connector P4   |

|                | CompactPCl® Serial Backplane Connector P5   |

|                | CompactPCl® Serial Backplane Connector P6   |

## About this Manual

This manual describes the technical aspects of the SC1-ALLEGRO, required for installation and system integration. It is intended for the experienced user only.

## **Edition History**

| Ed. | Contents/ <i>Changes</i>                                                                                                                                                         | Author | Date              |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------|

| 1   | User Manual SC1-ALLEGRO, english, preliminary edition Text #6782, File: sc1_ug.wpd                                                                                               | gn     | 2012-07-16        |

| 2   | Added photos                                                                                                                                                                     | jj     | 11 September 2012 |

| 3   | Changed name of DS_P to DS-P, removed the "not connected" note of 2 <sup>nd</sup> USB3 port on CompactPCI Serial connector P3, Memory Down and SO-DIMM are changed to PC3-12800. | gn     | 2012-11-09        |

| 4   | Added changes to PCH GPIO assignment coming with rev. 1                                                                                                                          | gn     | 2012-12-21        |

| 5   | Added illustration backplane resources                                                                                                                                           | jj     | 14 February 2013  |

| 6   | Changes to section "Serial ATA Interfaces"                                                                                                                                       | gn     | 2013-02-15        |

| 7   | Added recommendation regarding DisplayPort cable (pin 20 issue)                                                                                                                  | jj     | 5 March 2013      |

| 8   | Added photos, e.g. SC1 with PCS-BALLET Side Card, and BlueLine Small Systems Rack                                                                                                | jj     | 30 April 2013     |

| 9   | Removed display of JMB393 failures via red part of HD LED;<br>Added changes to CompactPCI Serial and J-HSE SATA assignments<br>coming with rev. 2                                | gn     | 2013-05-07        |

| 10  | Added Power Requirements                                                                                                                                                         | gn     | 2013-06-03        |

| 11  | Added MTBF                                                                                                                                                                       | gn     | 2013-06-04        |

| 12  | Corrected tables concerning DS-P switch in section "Configuration PCI Express Switch (DS-P)"                                                                                     | gn     | 2013-09-26        |

| 13  | Reworked section "Watchdog"                                                                                                                                                      | gn     | 2013-12-06        |

| 14  | Added Section "Board Control and Status Registers" Removed typo in table "P2 CompactPCI Serial Connector"                                                                        | gn     | 2014-08-07        |

| 15  | Added Power Requirements of SC1-041X                                                                                                                                             | gn     | 2014-09-29        |

| 16  | Additions to section "CompactPCI Serial"                                                                                                                                         | gn     | 2014-11-19        |

| 17  | Clarified resetting of UEFI BIOS settings to factory defaults                                                                                                                    | gn     | 2015-01-16        |

| 18  | Added comment to PCIe polarity inversion on table "P2 CompactPCI Serial Connector"                                                                                               | gn     | 2015-01-26        |

| 19  | Updated description of BCSR Control Register 0                                                                                                                                   | gn     | 2015-02-26        |

| 20  | Added illustration 'backplane resources' w. system slot right aligned, added photos SC1 with SCS-TRUMPET side card                                                               | jj     | 26 February 2015  |

| 21  | Updated description of BCSR Status Registers 0 and 1                                                                                                                             | gn     | 2015-04-01        |

| 22  | Cleaned up section "Watchdog"                                                                                                                                                    | gn     | 2015-04-07        |

| 23  | Updated LM87 Information                                                                                                                                                         | mib    | 2015-05-28        |

| 24  | Added photos SC1-ALLEGRO with C48-M2 mezzanine module                                                                                                                            | jj     | 28 May 2015       |

| Ed. | Contents/ <i>Changes</i>                                           | Author | Date            |

|-----|--------------------------------------------------------------------|--------|-----------------|

| 25  | Table 'Feature Summary' - added RTOS support                       | jj     | 1 October 2015  |

| 26  | Table 'Feature Summary' - added performance rating                 | jj     | 30 October 2015 |

| 27  | Marked backplane connector P1 pin G3 (SATA_SDI) as "not connected" | gn     | 2016-08-05      |

| 28  | Added Celeron® 1047UE processor to table 'Feature Summary'         | jj     | 31 March 2017   |

| 29  | Celeron® 1047UE as SKU processor in table 'Feature Summary'        | jj     | 6 April 2017    |

| 30  | Mixup fixed - MTBF valid for 40°C (not 50°C)                       | jj     | 4 October 2018  |

#### **Related Documents**

| Related Information SC1-ALLEGRO |                              |  |

|---------------------------------|------------------------------|--|

| SC1-ALLEGRO Home                | www.ekf.com/s/sc1/sc1.html   |  |

| SC1-ALLEGRO Product Information | www.ekf.com/s/sc1/sc1_pi.pdf |  |

#### Nomenclature

Signal names used herein with an attached '#' designate active low lines.

#### **Trade Marks**

Some terms used herein are property of their respective owners, e.g.

- ► Chief River, Ivy Bridge, Panther Point, Core i7: ® Intel

- CompactPCI, CompactPCI PlusIO, CompactPCI Serial: ® PICMG

- Windows XP, Windows 7: ® Microsoft

- ► EKF, ekf system: ® EKF

EKF does not claim this list to be complete.

## Legal Disclaimer - Liability Exclusion

This manual has been edited as carefully as possible. We apologize for any potential mistake. Information provided herein is designated exclusively to the proficient user (system integrator, engineer). EKF can accept no responsibility for any damage caused by the use of this manual.

Please note: If an EKF product has been labelled with contact support@ekf.com for availability of additional usage.

this special sign according to ISO 7010 M002, please documentation which may be important for proper

## Standards

| Reference Documents               |                                                                                                                                      |                                                          |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Term                              | Document                                                                                                                             | Origin                                                   |

| CFast™                            | CFast™ Specification Rev. 1.0                                                                                                        | www.compactflash.org                                     |

| CompactPCI <sup>®</sup>           | CompactPCI Specification, PICMG® 2.0 R3.0, Oct. 1, 1999                                                                              | www.picmg.org                                            |

| CompactPCl®<br>PlusIO             | CompactPCI PlusIO Specification, PICMG® 2.30 R1.0, November 11, 2009                                                                 | www.picmg.org                                            |

| CompactPCl <sup>®</sup><br>Serial | CompactPCI Serial Specification, PICMG® CPCI-S.0 R1.0, March 2, 2011                                                                 | www.picmg.org                                            |

| DisplayPort                       | VESA DisplayPort Standard Version 1.1a<br>January 11, 2008<br>VESA Mini DisplayPort Connector Standard Version 1<br>October 26, 2009 | www.vesa.org                                             |

| DVI                               | Digital Visual Interface Rev. 1.0 Digital Display Working Group                                                                      | www.ddwg.org                                             |

| Ethernet                          | IEEE Std 802.3, 2000 Edition                                                                                                         | standards.ieee.org                                       |

| LPC                               | Low Pin Count Interface Specification, Revision 1.1                                                                                  | developer.intel.com/design/<br>chipsets/industry/lpc.htm |

| HD Audio                          | High Definition Audio Specification Rev.1.0                                                                                          | www.intel.com/design/chipsets/<br>hdaudio.htm            |

| PCI Express®                      | PCI Express® Base Specification 3.0                                                                                                  | www.pcisig.com                                           |

| SATA                              | Serial ATA 2.5/2.6 Specification<br>Serial ATA 3.0 & 3.1 Specification                                                               | www.sata-io.org                                          |

| USB                               | Universal Serial Bus 3.0 Specification, Revision 1.0<br>November 12, 2008                                                            | www.usb.org                                              |

#### Overview

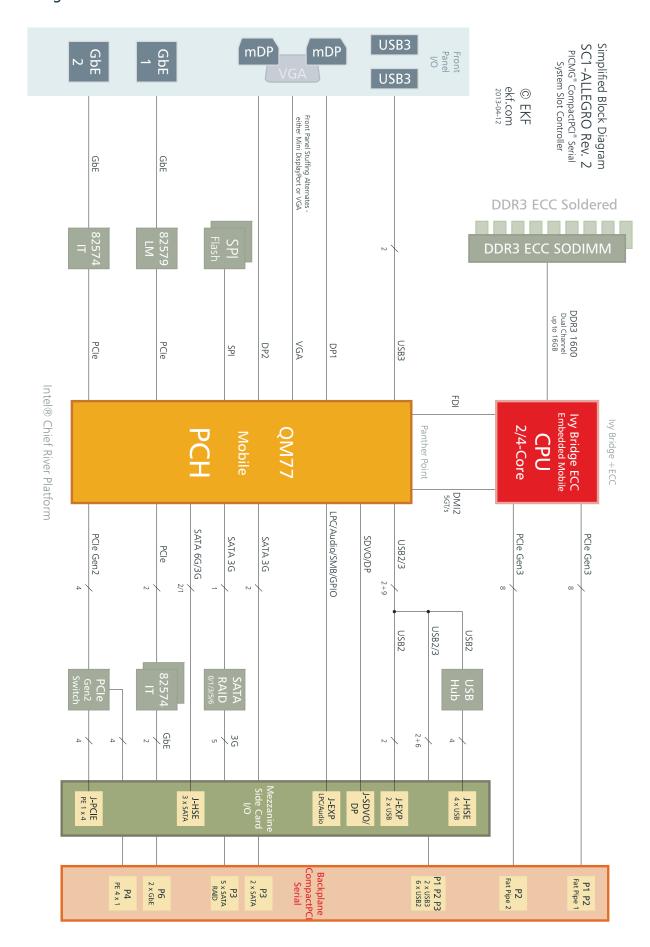

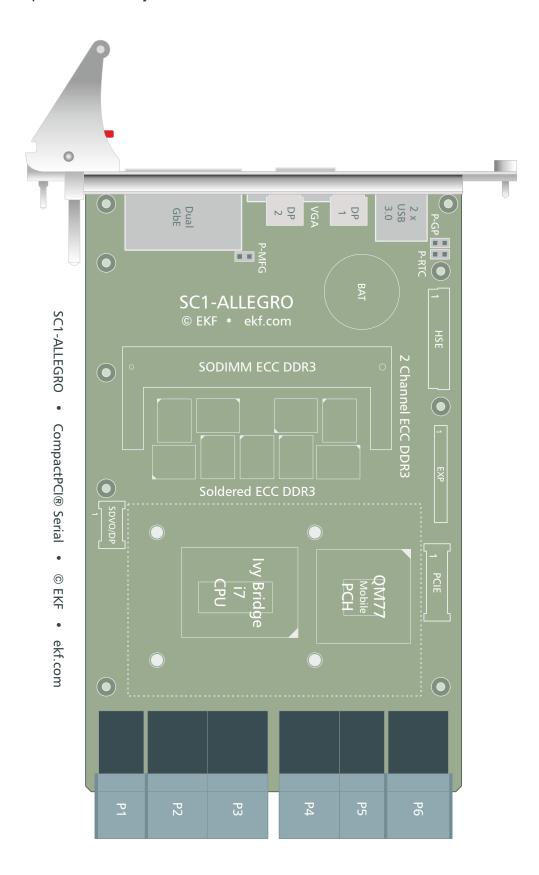

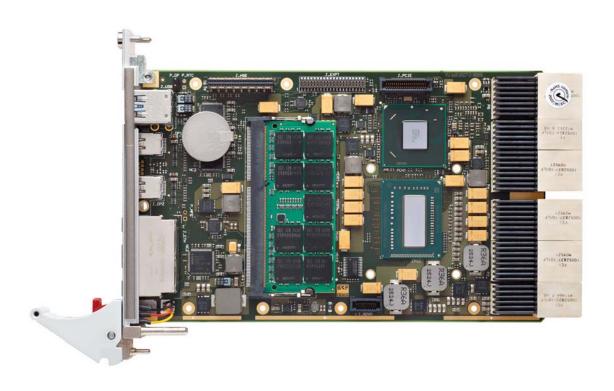

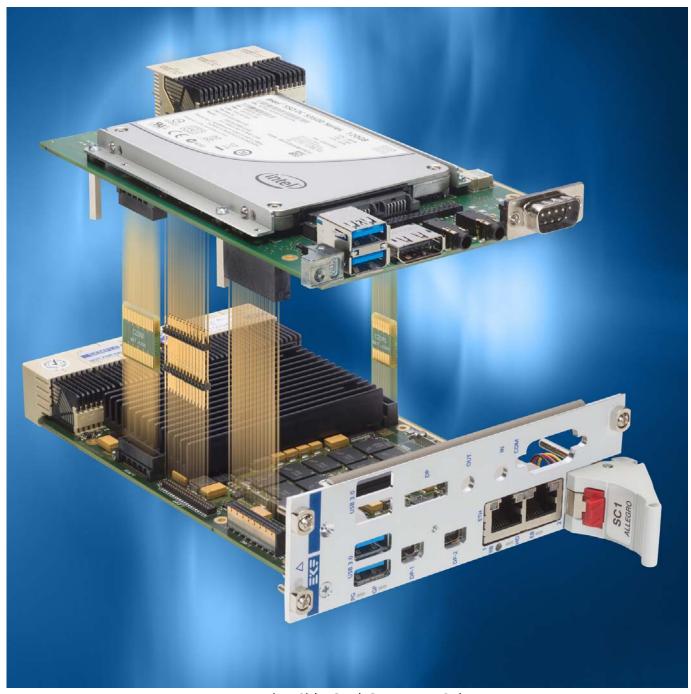

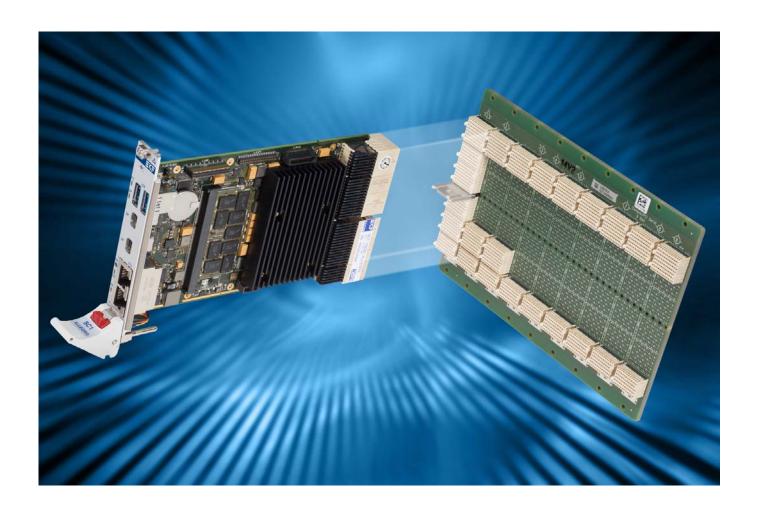

The SC1-ALLEGRO is a rich featured high performance 4HP/3U CompactPCl® Serial CPU board, equipped with an Intel® Core™ i7 Mobile 3<sup>rd</sup> Generation + ECC (dual- or quadcore) processor based on 22nm technology. The SC1-ALLEGRO front panel is provided with two Gigabit Ethernet jacks, two USB 3.0 receptacles, and two Mini-DisplayPort connectors for attachment of high resolution digital displays, configured e.g. as extended desktop.

The SC1-ALLEGRO is equipped with up to 16GB RAM with ECC support. 8GB memory-down are provided for rugged applications, and another 8GB are available via the DDR3 ECC SO-DIMM socket. As an option, a low profile mezzanine module with dual mSATA SSDs may serve as a high-speed RAID mass storage solution. The SC1-ALLEGRO backplane connectors comply with the PICMG® *CompactPCl*® Serial system slot specification.

While mechanically compliant to *CompactPCl*<sup>®</sup> Classic, *CompactPCl*<sup>®</sup> Serial (PICMG® CPCIS.0) defines a completely new card slot, based on PCI Express®, SATA, Gigabit Ethernet and USB serial data lines. Up to 6 high-speed backplane connectors P1 - P6 are provided on a system slot controller such as the SC1-ALLEGRO, which can be considered as a root hub with respect to most signal lines. A passive backplane is used for distribution of a defined subset of I/O channels from the system slot to each of up to eight peripheral slots in a *CompactPCl*<sup>®</sup> Serial system.

Most *CompactPCl*® Serial peripheral slot cards require only the backplane connector P1, which comprises PCle, SATA and USB signals, resulting in a concise and inexpensive peripheral board design. More powerful peripheral cards profit from so called Fat Pipe slots (PCle x 8).

The SC1-ALLEGRO is a native *CompactPCl*<sup>®</sup> Serial CPU card, suitable for usage in a pure CPCI Serial environment. Due to its generous backplane capabilities (20 x PCI Express® lanes, 6 x USB, 7 x SATA/RAID, 2 x GbE), very powerful industrial systems can be built.

The SC1-ALLEGRO is equipped with a set of local expansion interface connectors, which can be optionally used to attach a mezzanine side board. A variety of expansion cards is available, e.g. providing legacy I/O and additional PCI Express® based I/O controllers such as SATA, USB 3.0 and Gigabit Ethernet, or a third video output. Most mezzanine side cards can accommodate in addition a 2.5-inch drive.

Typically, the SC1-ALLEGRO and the related side card would come as a readily assembled 8HP unit. As an alternate, low profile Flash based mezzanine storage modules are available that fit on the SC1-ALLEGRO while maintaining the 4HP profile. The C42-SATA module e.g. is equipped with a very fast 1.8-inch SATA Solid State Drive (SSD), which is suitable for installation of any popular operating system.

| Related Documents CompactPCI® PlusIO & CompactPCI® Serial |                                  |  |

|-----------------------------------------------------------|----------------------------------|--|

| CompactPCI® Serial - Concise Guide                        | www.ekf.com/s/serial_concise.pdf |  |

| CompactPCI® Serial - The Smart Solution                   | www.ekf.com/s/smart_solution.pdf |  |

| CompactPCI® Serial Home                                   | www.ekf.com/s/serial.html        |  |

| CompactPCI® PlusIO Home                                   | www.ekf.com/p/plus.html          |  |

#### **Technical Features**

## Feature Summary

## **Feature Summary**

- CompactPCP Serial (PICMG® CPCI-S.0) System Slot Controller

- ▶ Based on the Intel® *Chief River* Platform (*Ivy Bridge + ECC* CPU, *Panther Point* PCH)

- Intel® Core™ i7 (i5/i3) Mobile 3<sup>rd</sup> Generation ECC Processor, 22nm Process Technology, Low Power, Dual-Core and Quad-Core, Code Name *Ivy Bridge*

- ▶ i7-3612QE Processor 2.1GHz 35W TDP Standard Voltage Quad-Core

- ▶ i7-3555LE Processor 2.5GHz 25W TDP Low Voltage Dual-Core

- i7-3517UE Processor 1.7GHz 17W TDP Ultra Low Voltage Dual-Core

- ▶ i5-3610ME Processor 2.7GHz 35W TDP Standard Voltage Dual-Core

- i3-3120ME Processor 2.4GHz 35W TDP Standard Voltage Dual-Core

- i3-3217UE Processor 1.6GHz 17W TDP Ultra Low Voltage Dual-Core

- Celeron® 1047UE Processor 1.4GHz 17W TDP Ultra Low Voltage Dual-Core

- Integrated HD Graphics Engine, 3 Independent Displays, Enhanced Media Processing

- ▶ Integrated Memory Controller up to 16GB DDR3 +ECC 1333 and 1600

- ▶ DDR3 +ECC Soldered Memory up to 8GB

- ▶ DDR3 +ECC SO-DIMM Memory Module Socket up to 8GB

- Performance Rating Passmark 8.0 SC1-680D (i7-i7-3612QE): Passmark Rating 2241, CPU Rating 7243

- Intel® QM77 Platform Controller Hub (PCH), Code Name Panther Point

- Up to 3 Display Configuration (Front Panel: Dual mDP or Single VGA Connector Option)

- Max Resolution 2560 x 1600 (DisplayPort), 1920 x 1200 (VGA)

- 2 + 1 SATA Channels 6Gbps/3Gbps for Mezzanine Storage Modules (Connector HSE)

- CompactFlash® Card with C40-SCFA Mezzanine Module Option (4HP Maintained)

- ► CFast™ Card with C41-CFAST Mezzanine Module Option (4HP Profile Maintained)

- SATA 1.8-Inch Solid State Drive with C42-SATA Mezzanine Card Option (4HP Maintained)

- Dual mSATA Modules with C47-MSATA RAID Mezzanine Card Option (4HP Maintained)

- Dual M.2 SATA SSD Modules with C48-M2 RAID Mezzanine Card Option (4HP Maintained)

- 7 x SATA Channels 3Gbps to Backplane Connectors, 5 Channels Available for Hardware RAID Configuration Level 0/1/10 + Hot Spare (Option RAID Level 3/5)

- ▶ 4 x USB 3.0 XHCI SuperSpeed Channels (2 x to F/P Connectors, 2 x Backplane)

- ▶ 10 x USB 2.0 EHCI (6 x to Mezzanine Connectors, 4 x Backplane)

- ▶ 4 x Gigabit Ethernet Controllers (2 x F/P RJ-45 Jacks and 2 x Backplane Connector)

- ▶ 8 + 8 x PCI Express® Gen3 Lanes to CPCI Serial Backplane (CPCI Serial Fat Pipe 1 + 2)

- ► 4 + 4 x PCI Express® Gen2 Lanes (4 x Mezzanine Connector, 4 x Backplane)

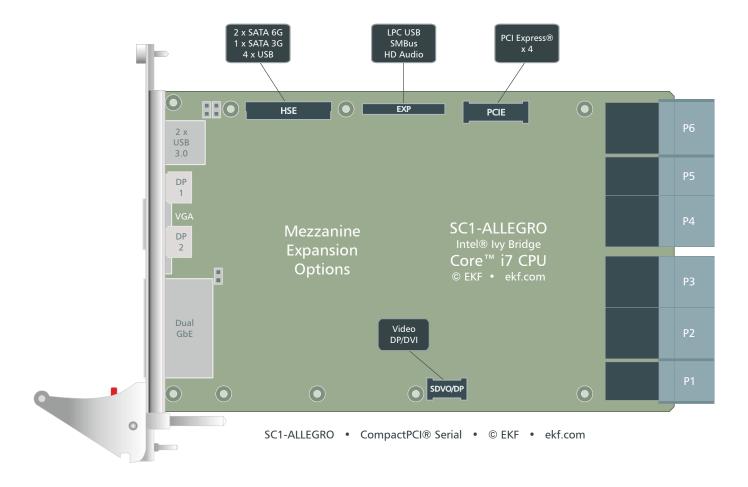

- Legacy I/O Mezzanine Expansion Connector EXP (USB, HD Audio, LPC)

- ► High Speed I/O Mezzanine Expansion Connector HSE (3 x SATA, 4 x USB)

- ► PCI Express® Mezzanine Expansion Connector PCIE (4 Lanes)

- Third Display Mezzanine Expansion Connector SDVO/DP

- Variety of Mezzanine Expansion Boards (Side Cards) Available with and w/o PCIe

- Most Mezzanines Optionally Equipped with 2.5-Inch Single- or Dual-Drive

- UEFI Phoenix BIOS with ACPI

- Long Term Availability

- Coating, Sealing, Underfilling on Request

- RoHS compliant

- Designed & Manufactured in Germany

- ▶ ISO 9001 Certified Quality Management System

- RT OS BSP & Driver Support VxWorks 7.0 Available, QNX and Others on Request

## **Operating Conditions**

| Operating Conditions               |                                                                                                                                                                                                                                                                                                               |  |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Thermal & Environmental Conditions | <ul> <li>▶ Operating Temperature 0°C to +70°C (-40°C to +85°C on Request)</li> <li>▶ Storage temperature: -40°C to +85°C, max. Gradient 5°C/min</li> <li>▶ Humidity 5% 95% RH non Condensing</li> <li>▶ Altitude -300m +3000m</li> <li>▶ Shock 15g 0.33ms, 6g 6ms</li> <li>▶ Vibration 1g 5-2000Hz</li> </ul> |  |

| EC Regulations                     | ► EN55022, EN55024, EN60950-1 (UL60950-1/IEC60950-1)  ► 2002/95/EC (RoHS)                                                                                                                                                                                                                                     |  |

| MTBF                               | 104 x 10 <sup>3</sup> h (11.9 years) @ 40° C                                                                                                                                                                                                                                                                  |  |

## **Power Requirements**

| Power Requirements |                                                               |                                                   |  |

|--------------------|---------------------------------------------------------------|---------------------------------------------------|--|

|                    | Load Current [A] at +12V (±5%)                                |                                                   |  |

| Board              | Maximum Performance<br>LFM / HFM / Turbo <sup>1)</sup>        | Windows 7 Idle<br>LFM / HFM / Turbo <sup>1)</sup> |  |

| SC1-68XX           | 3.8 / 4.0 / 4.5 2)                                            | 1.0 / 1.0 / 1.0 2)                                |  |

| SC1-42XX           | 2.6 / 3.2 / 3.4 2)                                            | 1.0 / 1.0 / 1.0 2)                                |  |

| SC1-22XX           | 2.5 / 2.6 / 2.6 2)                                            | 1.0 / 1.0 / 1.0 2)                                |  |

| SC1-041X           | 1.4 / 1.7 / NA                                                | 1.0 / 1.0 / NA                                    |  |

|                    | Load Current [A] at +5V[STDBY] (±5%) 3)                       |                                                   |  |

|                    | Full On / Sleep / Hibernate / Soft Off<br>(S0 / S3 / S4 / S5) | 0/0/0/0.1                                         |  |

<sup>&</sup>lt;sup>1)</sup> Intel SpeedStep Frequence Modes LFM: Low Frequency Mode, HFM: High Frequency Mode. <sup>2)</sup> Add 60/200mA (link only/active) @1Gbps per Ethernet Port. <sup>3)</sup> This power supply is optional. It can be left open if not available.

## **Block Diagram**

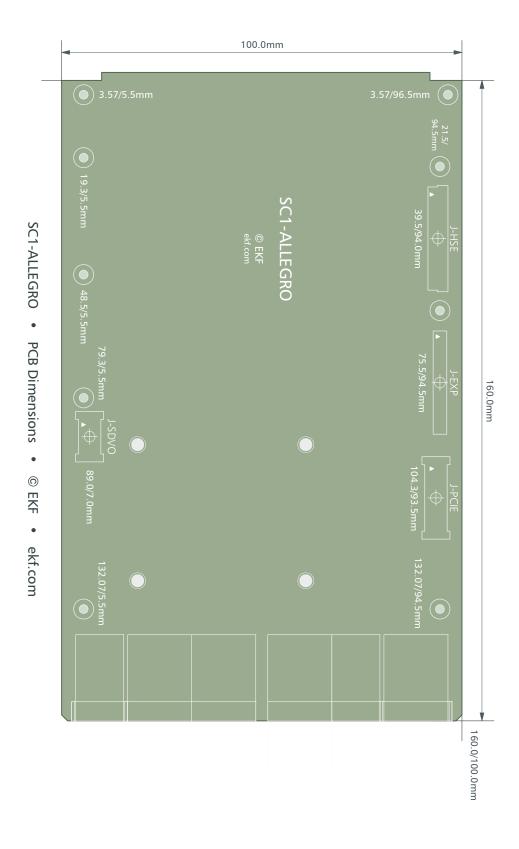

## **Top View Component Assembly**

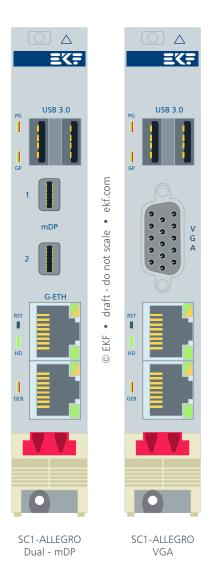

## **Front Panel Connectors**

| ETH1/2 | Dual Gigabit Ethernet RJ-45 receptacles with integrated indicator LEDs                  |

|--------|-----------------------------------------------------------------------------------------|

| mDP1/2 | Mini DisplayPort digital video output receptacle (VGA connector available as alternate) |

| USB1/2 | Universal Serial Bus 3.0 type A receptacles                                             |

| VGA    | VGA analog video output connector (Mini DisplayPort connectors available as alternate)  |

## Front Panel Switches & Indicators

| EB  | LED indicating Backplane Ethernet activity                                                       |

|-----|--------------------------------------------------------------------------------------------------|

| FPH | Front Panel Handle with integrated switch (programmable function, power event button by default) |

| GP  | General Purpose bicolour LED                                                                     |

| HD  | LED indicating any activity on SATA ports                                                        |

| PG  | Power Good/Board Healthy bicolour LED                                                            |

| RST | System Reset Button (Option)                                                                     |

## **On-Board Connectors & Sockets**

| J-EXPT<br>J-EXPB 1) | Utility EXPansion Interface Connector (LPC, USB, HD Audio, SMBus), available either from top (T) or bottom (B) 1) of the board, interface to optional side board |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J-HSE               | High Speed Expansion Connector (3 x SATA, 4 x USB), interface to optional low profile mezzanine module or side board                                             |

| J-PCIE              | PCI Express® Expansion Interface Connector, interface to optional side board                                                                                     |

| J-SDVO              | Digital Display Interface Connector (SDVO/DisplayPort)                                                                                                           |

| P1                  | CompactPCl® Serial Type A Connector                                                                                                                              |

| P2-P4               | CompactPCl® Serial Type B Connectors                                                                                                                             |

| P5                  | CompactPCl® Serial Type C Connector                                                                                                                              |

| P6                  | CompactPCl <sup>®</sup> Serial Type D Connector                                                                                                                  |

| SODM1               | 204-pin DDR3 ECC Memory Module SDRAM PC3-12800 Socket (ECC SODIMM)                                                                                               |

| XDP                 | CPU Debug Port 1)                                                                                                                                                |

<sup>&</sup>lt;sup>1)</sup> Connector populated on customers request only

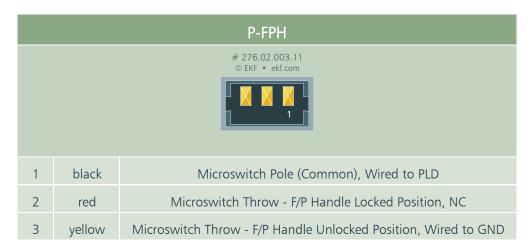

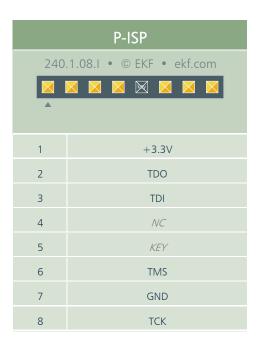

## Pin Headers

| P-FPH | Pin header suitable for Front Panel Handle switch cable harness |

|-------|-----------------------------------------------------------------|

| P-ISP | PLD glue logic device programming connector, not populated      |

## Jumpers

| DS-P  | Switches to configure link width and speed on J-PCIE       |

|-------|------------------------------------------------------------|

| P-GP  | Jumper to reset UEFI BIOS Setup to EKF Factory Defaults    |

| P-MFG | Jumper to enter Manufacturing Mode, not populated          |

| P-RTC | Jumper to reset RTC circuitry (part of PCH), not populated |

## Microprocessor

The SC1-ALLEGRO is equipped with Intel®  $Core^{TM}$  i7 or i5 3<sup>rd</sup> generation mobile ECC processor (code name Ivy Bridge). These low power processors provide integrated graphics and memory controller, which results in a very efficient platform design. The  $Core^{TM}$  processors almost can be considered as a single-chip solution, since all functions of a typical north-bridge have been moved to the CPU.

The Core<sup>TM</sup> i7 and i5 processor family includes beside the Standard-Voltage (SV) also several Ultra Low-Voltage (ULV) and Low-Voltage (LV) processors as listed below. The processors are housed in a Micro FC-BGA package for direct soldering to the PCB, i.e. the chip cannot be removed or changed by the user.

The processors supported by the SC1-ALLEGRO are running at core clock speeds up to 2.1GHz for quad core and up to 2.5GHz on dual core devices. Due to Enhanced Intel® SpeedStep® and Intel® Turbo Boost Technology each core can decrease or increase its nominal operating frequency. The clock speed is chosen depending on the power states of the processor cores/graphics engine, the currently required performance, and the actual core temperature.

Power is applied across the *CompactPCI*<sup>®</sup> connector P1 (12V). The processors core and graphics voltages are generated by switched voltage regulators according to Intels IMVP-7 voltage regulator specification.

| Intel® Core™ Processors Supported |                   |                         |       |              |                   |     |        |          |              |

|-----------------------------------|-------------------|-------------------------|-------|--------------|-------------------|-----|--------|----------|--------------|

| Processor<br>Number               | Physical<br>Cores | Core Clock<br>nom./max. | Cache | Gfx<br>Clock | Junction<br>Temp. | TDP | CPU ID | Stepping | SPEC<br>Code |

| i7-3612QE                         | 4                 | 2.1/3.1GHz              | 4MB   | 650MHz       | +105°C            | 35W | 306A9h | E-1      | SROND        |

| i7-3555LE                         | 2                 | 2.5/3.2GHz              | 4MB   | 550MHz       | +105°C            | 25W | 306A9h | L-1      | SR0T5        |

| i7-3517UE                         | 2                 | 1.7/2.8GHz              | 4MB   | 350MHz       | +105°C            | 17W | 306A9h | L-1      | SR0T6        |

| i5-3610ME                         | 2                 | 2.7/3.3GHz              | 3MB   | 650MHz       | +105°C            | 35W | 306A9h | L-1      | SROQK        |

#### Thermal Considerations

In order to avoid malfunctioning of the SC1-ALLEGRO, take care of appropriate cooling of the processor and system, e.g. by a cooling fan suitable to the maximum power consumption of the CPU chip actually in use. The processor contains digital thermal sensors (DTS) that are readable via special CPU registers. DTS allows to get the temperatures of each CPU core separately.

Two further temperature sensors, located in the system hardware monitor LM87, allows for acquisition of the boards surface temperature and the thermal state of the onboard system memory channel. Beside this the LM87 also monitors most of the supply voltages. A suitable software on Microsoft Windows® systems to display both, the temperatures as well as the supply voltages, is Speedfan, which can be downloaded from the web. After installation, both temperatures and voltages can be observed permanently from the Windows® taskbar.

The SC1-ALLEGRO is equipped with a passive heatsink. Its height takes into account the 4HP limitation in mounting space of a  $CompactPCl^{\circ}$  board. In addition, a forced vertical airflow through the system enclosure (e.g. bottom mount fan unit) is strongly recommended (>20m³/h or 2m/s (400LFM) around the CPU slot). Be sure to thoroughly discuss your actual cooling needs with EKF. Generally, the faster the CPU speed the higher its power consumption. For higher ambient temperatures, consider increasing the forced airflow to 3m/s (600LFM) or more.

The table showing the supported processors above give also the maximum power consumption (TDP = Thermal Design Power) of a particular processor. Fortunately, the power consumption is by far lower when executing typical Windows® or Linux tasks. The heat dissipation increases when e.g. rendering software like the Acrobat Distiller is executed.

The Core<sup>™</sup> i7 processors support Intel's Enhanced SpeedStep® technology. This enables dynamic switching between multiple core voltages and frequencies depending on core temperature and currently required performance. The processors are able to reduce their core speed and core voltage in multiple steps down to 1200MHz (800MHz for LV/ULV processors). Additional a reduction of the graphics core clock and voltage is possible. This leads to an obvious reduction of power consumption resulting in less heating. This mode of lowering the processor core temperature is called TM2 (TM=Thermal Monitor).

Another way to reduce power consumption is to modulate the processor clock. This mode (TM1) is achieved by actuating the 'Stop Clock' input of the CPU. A throttling of 50% e.g. means a duty cycle of 50% on the stop clock input. However, while saving considerable power consumption, the data throughput of the processor is also reduced. The processor works at full speed until the core temperature reaches a critical value. Then the processor is throttled by 50%. As soon as the high temperature situation disappears the throttling will be disabled and the processors runs at full speed again.

These features are controllable by BIOS menu entries. By default the BIOS of the SC1-ALLEGRO enables mode TM2 which is the most efficient.

### Main Memory

The SC1-ALLEGRO features two channels of DDR3 SDRAMs with support of ECC (Error Correction Code). One channel is realized with 18 memory devices soldered to the board (Memory Down) and delivers a capacity of up to 8GB with a clock frequency of 1600MHz (PC3-12800).

The 2nd channel provides a socket for installing a 204-pin ECC SODIMM module thus allowing a simple expansion of system memory (max. module height = 1.25 inch). Supported are unbuffered DDR3 ECC SODIMMs (72-bit) with  $V_{DD}$ =1.5V featuring on-die termination (ODT), according the PC3-12800 specification. Minimum module size is 512MB; maximum module size is 8GB. Please note that standard DDR3 SODIMMs without ECC feature do not work on SC1-ALLEGRO.

It is recommended to add a SODIMM module with same size as the Memory Down to get best performance (some of the system memory is dedicated to the graphics controller). This typically results in a size of 2x4GB of memory which is recommended to run the operating systems Windows® Vista or Windows® 7.

The memory controller supports symmetric and asymmetric memory organization. The maximum memory performance can be obtained by using the symmetric mode. When in this mode, the memory controller accesses the memory channels in an interleaved way. Since Core<sup>TM</sup> i7 processors support Intels Flex Memory Technology, interleaved operation isn't limited to systems using memory channels of equal capacity. In the case of unequal memory population the smaller memory channel dictates the address space of the interleaved accessible memory region. The remainder of the memory is then accessed in non-interleaved mode.

In asymmetric mode the memory always will be accessed in a non-interleaved manner with the drawback of less bandwidth. The only meaningful application of asymmetric mode is the special case when only one memory channel is populated (i.e. the SODIMM socket may be left empty).

The contents of the SPD EEPROM on the SODIMM is used by the BIOS at POST (Power-on Self Test) to get any necessary timing parameters to program the memory controller within the chipset.

## **Graphics Subsystem**

The graphics subsystem is part of the Intel Core<sup>™</sup> i7 processor and the PCH QM77. While the graphics controller is located within the Core<sup>™</sup> i7 processor, the different interfaces like DisplayPort, SDVO and VGA are moved to the PCH. The SC1-ALLEGRO offers two Mini DisplayPort (mDP) interfaces in the front panel.

Adapters to convert Mini DisplayPort to any other popular interface standard are available.

A 3<sup>rd</sup> DisplayPort or an SDVO port is fed in a multiplexed manner to the on-board connector J-SDVO. EKF expansion boards like PCS-BALLET feature the possibility to gain access to the 3<sup>rd</sup> DisplayPort interface. Additionally EKF offers a bundle of expansion boards that contain a display transmitter to provide a DVI channel via a pure digital DVI-D connector.

As an option, the SC1-ALLEGRO can be equipped with an ordinary HD D-Sub 15-lead connector (VGA style). This connector is suitable for analog signals only. Nevertheless also flat-panel displays can be attached to the D-Sub connector but with minor reduced image quality.

Independent from the video connector actually in use, Mini DisplayPort, DVI or VGA, the VESA DDC standard is supported. This allows to read out important parameters, e.g. the maximum allowable resolution, from the attached monitor. DDC Power, +3.3V or +5V on DisplayPort or VGA connector respectively, is delivered via a resettable fuse to protect the board from an external short-circuit condition (0.5A).

Graphics drivers for the Core<sup>™</sup> i7 can be downloaded from the Intel web site.

### LAN Subsystem

The Ethernet LAN subsystem is composed of four Gigabit Ethernet ports: One Intel 82579LM Physical Layer Transceiver (PHY) using the PCH QM77 internal MAC and three Intel 82574IT Gigabit Ethernet Controllers. These devices provide also legacy 10Base-T and 100Base-TX connectivity. Two of the Ethernet ports are fed to two RJ45 jacks located in the front panel, the others are attached to the CompactPCl® Serial interface on P6. Each port includes the following features:

- ► One PCI Express lane per Ethernet port (250MB/s)

- ▶ 1000Base-Tx (Gigabit Ethernet), 100Base-TX (Fast Ethernet) and 10Base-T (Classic Ethernet) capability.

- ► Half- or full-duplex operation.

- ► IEEE 802.3u, 802.3ab Auto-Negotiation for the fastest available connection.

- Jumperless configuration (complete software-configurable).

Two bicoloured LEDs integrated into the dedicated RJ-45 connector in the front panel are used to signal the LAN link, the LAN connection speed and activity status. A further bicoloured LED in front panel labelled EB displays the state of the backplane network ports.

Each device is connected by a single PCI Express lane to the PCH. Their MAC addresses (unique hardware number) are stored in dedicated FLASH/EEPROM components. The Intel Ethernet software and drivers for the 82579 and 82574 is available from Intel's World Wide Web site for download.

When managing the board by Intel Active Management Technology (iAMT), the dedicated network port to do so is accessible by the RJ45 connector GbE1 (the upper port within the front panel).

### Serial ATA Interface (SATA)

The SC1-ALLEGRO provides a total of ten serial ATA (SATA) ports, derived from two independent SATA controllers. Two of these ports support data transfer rates of 6Gbps (600MB/s) while all ports are capable to work with 3Gbps (300MB/s) or 1.5Gbps (150MB/s). The SATA controllers are located within the QM77 Platform Controller Hub that holds 6 SATA interfaces.

The two 6Gbps and one 3Gbps ports are fed to the high speed expansion connector J-HSE. This connector allows the installation of low profile expansion boards like C41-CFAST or C42-SATA to attach the popular CFast cards or Micro SATA SSDs (1.8-inch) respectively. Another mezzanine is the C47-MSATA, a carrier for two mSATA SSD modules, that is connected via J-HSE to the 6Gbps ports for fast data storage. Also consider the C48-M2 mezzanine for mass storage, which can accommodate two M.2 style SATA SSD modules.

Another of the 3Gbps ports is fed from the QM77 to a JMicron JMB393 6-port RAID controller supporting RAID levels 0/1/3/5/10 as well as JBOD and CLONE. Five of the JMB393 ports as well as the two remaining QM77 ports are used to supply the *CompactPCl*<sup>®</sup> Serial SATA interfaces on the backplane.

A LED named HD located in the front panel, signals disk activity status of any of the SATA devices.

Additionally a variety of side cards is available, suitable for mounting on the SC1-ALLEGRO in a 4HP (20.32mm) distance (resulting in 8HP front panel width for the assembly). Some of these side boards can accommodate a SATA drive, e.g. a 2.5-inch SSD.

Available for download from Intel's web site are drivers for popular operating systems, e.g. Windows® XP, Windows® 7 and Linux.

To manage the RAID configuration of the JMB393 a Windows® application is provided by JMicron that can be downloaded from EKF's website.

## PCI Express® Interface

The SC1-ALLEGRO is provided with several PCI Express (PCIe) lanes for I/O expansion. Sixteen PCI Express lanes, originating from the  $Core^{TM}$  i7 processor, are building the two fat pipes defined by  $CompactPCl^{\oplus}$  Serial. These two links consists of eight lanes with transfer rates of up to 8Gbps (PCI Express Gen 3).

The QM77 offers a total of eight PCI Express ports supporting PCIe Gen 2 speed (5GT/s). Four of them form the upstream link to a PCI Express switch. The output ports (downstream ports) of the PCIe switch are connected to the *CompactPCI*<sup>®</sup> Serial connector P4 (four lanes) and to the local PCIe expansion interface connector J-PCIE (four lanes).

Two small DIP switches (DS-P) located on the backside of the board are used to configure different lane widths to each of both downstream interfaces and to choose the interface transfer rate. Possible settings are

- ► Four links x 1 lane to CompactPC® Serial P4 and a single link x 4 lanes to J-PCIE

- ► Four links x 1 lane to CompactPCl® Serial P4 and four links x 1 lane to J-PCIE

- 2.5GT/s or 5GT/s transfer speed

See section "Configuration PCI Express Switch (DS-P)" for details.

### Universal Serial Bus (USB)

The SC1-ALLEGRO is provided with fourteen USB ports. All of them are USB 2.0 capable, but four ports are also supporting the USB 3.0 SuperSpeed standard. Two USB 3.0 interfaces are routed to front panel connectors, the other two SuperSpeed ports are feed to the *CompactPCl*<sup>®</sup> Serial connectors P1 and P3.

The USB 2.0 interfaces are distributed to the front panel (two ports), two to the expansion board interface connectors J-EXP, four to the high speed expansion connector J-HSE, and six ports are available across the backplane connectors for *CompactPCl*<sup>®</sup> Serial.

The front panel USB connectors can source a minimum of 1.5A/5V each, over-current protected by two electronic switches. Protection for the USB ports on the expansion interfaces and on the *CompactPCl*® Serial connectors is located on expansion boards and the boards on the *CompactPCl*® Serial backplane respective. The USB xHCl and two EHCl controllers handling the USB port operation at SuperSpeed, high-speed, full-speed and low-speed are integrated into the QM77 PCH.

## **Utility Interfaces**

Besides the high speed mezzanine interface connectors J-HSE and J-PCIE, the SC1-ALLEGRO is provided with the utility interface expansion connector socket J-EXP. This connector comprises several interfaces, which may be useful for system expansion on mezzanine cards, as an option:

- HD Audio

- ► LPC (Low Pin Count)

- ► SMBus

- ▶ 2 x USB

The SMBus is controlled by the QM77 platform controller hub. The SMBus signal lines on the J-EXP utility expansion connector can be switched on/off under software control (PCH GPIO) in order to isolate external components in case of an I<sup>2</sup>C address conflict.

The HD Audio port requires an additional audio codec, as provided e.g. on the CCO-CONCERT side card.

The LPC bus presents an easy way to add legacy interfaces to the system. EKF offers a variety of mezzanine expansion boards (side cards), to be attached on top of the SC1-ALLEGRO, featuring all classic Super-I/O functionality, for example the CCO-CONCERT. Access to the connectors PS/2 (mouse, keyboard), COM, USB and audio in/out is given directly from the front panel.

#### Real-Time Clock

The SC1-ALLEGRO has a time-of-day clock and 100-year calendar, integrated into the QM77 PCH. A battery on the board keeps the clock current when the computer is turned off. The SC1 uses a BR2032 lithium battery soldered in the board, giving an autonomy of more than 5 years. Under normal conditions, replacement should be superfluous during lifetime of the board.

In applications were the use of a battery is not permitted, a SuperCap can be stuffed instead of the battery.

### SPI Flash

The BIOS and iAMT firmware is stored in flash devices with Serial Peripheral Interface (SPI). Up to 16MByte of BIOS code, firmware and user data may be stored nonvolatile in these SPI Flashes.

The SPI Flash contents can be updated by a DOS or Linux based tool. This program and the latest SC1-ALLEGRO BIOS binary are available from the EKF website. Read carefully the enclosed instructions. If the programming procedure fails e.g. caused by a power interruption, the SC1-ALLEGRO may no more be operable. In this case you would possibly have to send in the board, because the Flash device is directly soldered to the PCB and cannot be changed by the user.

#### Reset

The SC1-ALLEGRO is provided with several supervisor circuits to monitor supply rails like the CPU core voltage, 1.5V, 3.3V or 5V. This circuitry is responsible also to generate a clean power-on reset signal.

To force a manual board reset, the SC1-ALLEGRO offers a small tactile switch within the front panel. This push-button is indent mounted and requires a tool, e.g. a pen to be pressed, preventing from being inadvertently activated.

The handle within the front panel contains a micro switch that is used to generate a power button event. By pressing the handle's red push button a pulse is triggered.

Animated GIF: www.ekf.com/c/ccpu/img/reset 400.gif

<u>NOTE:</u> To prevent the board to cause a power button override, the handle should be closed immediately after unlocking the front panel handle. A power button override is triggered by opening the front panel handle for at least 4 seconds, which results in bringing the board to power state S5. In case of entering this state, unlock and lock the front panel handle a 2<sup>nd</sup> time to reenter normal power state S0 again. See also section 'PG (Power Good) LED' to see how the SC1-ALLEGRO indicates the different power states.

<u>WARNING:</u> The SC1-ALLEGRO will enter the power state S5 if the front panel handle is not closed properly when the system powers up. An open handle is signalled by a yellow blinking 'PG LED'.

The manual reset push-button and the power button functionality of the front panel handle could be passivated by BIOS settings.

An alternative (and recommended) way to generate a system reset is to activate the signal PRST# located on *CompactPCl*® Serial connector P1 pin H2. Pulling this signal to GND will have the same effect as to push the tactile reset switch.

The healthy state of the SC1-ALLEGRO is indicated by the LED PG (Power Good) located in the front panel. This bicoloured LED signals different states of the board (see section below). As soon as this LED begins to lite green, all power voltages are within their specifications and the reset signal has been deasserted.

© EKF • ekf.com

## Watchdog

An important reliability feature is a software programmable watchdog function. The SC1-ALLEGRO contains two of these watchdogs. One is part of the QM77 PCH and also known as TCO Watchdog. A detailed description is given in the QM77 data sheet. Operating systems like Linux offer a driver interface to the TCO watchdog.

The behaviour of the 2<sup>nd</sup> watchdog is defined within a PLD of the SC1, which activates/deactivates the watchdog and controls its time-out period. The time-out delay is adjustable in the steps 2, 10, 50 and 255 seconds. After alerting the WD and programming the time-out value, the related software (e.g. application program) must trigger the watchdog periodically. For details on programming the watchdog see section "Board Control and Status Register (BCSR)".

This watchdog is in a passive state after a system reset. There is no need to trigger it at boot time. The watchdog is activated on the first trigger request. If the duration between two trigger requests exceeds the programmed period, the watchdog times out and a full system reset will be generated. The watchdog remains in the active state until the next system reset. There is no way to disable it once it has been put on alert, whereas it is possible to reprogram its time-out value at any time.

### Front Panel LEDs

The SC1-ALLEGRO is equipped with four LEDs which can be observed from the front panel. Three of these LEDs are labelled according to their primary meaning, but should be interpreted altogether for system diagnosis:

| LED             |                 |                 |                                            |

|-----------------|-----------------|-----------------|--------------------------------------------|

| PG<br>Green/Red | GP<br>Green/Red | HD<br>Green/Red | Status                                     |

| OFF             | GREEN           | GREEN           | Sleep State S5 (Soft Off)                  |

| OFF             | GREEN           | OFF             | Sleep State S4 (Suspend to Disk/Hibernate) |

| OFF             | OFF             | GREEN           | Sleep State S3 (Suspend to RAM/Standby)    |

| GREEN           | RED BLINK       | X               | After Reset                                |

| GREEN           | X               | X               | Board Healthy and in SO State              |

| YELLOW BLINK    | X               | X               | Front panel handle is unlocked             |

| RED             | X               | X               | Hardware Failure - Power Fault             |

| RED BLINK       | X               | X               | Software Failure                           |

### PG (Power Good) LED

The SC1-ALLEGRO offers a bicolour LED labelled PG located within the front panel. After system reset, this LED defaults to signal different power states:

Off Sleep state S3, S4 or S5

Green Healthy

Yellow blink Front panel handle open

Red steady Hardware failureRed blink Software failure

To enter the PG LED state *Software Failure*, the bit PGLED in the board control register CTRLL\_REG must be set. The PG LED remains in this red blinking state until this bit is cleared. After that it falls back to its default function.

### GP (General Purpose) LED

This programmable bicolour LED can be observed from the SC1-ALLEGRO front panel. The status of the red part within the LED is controlled by the GPIO18 of the PCH QM77. Setting GPIO18 to "1" will switch on the red LED. Turning on or off the green LED is done by setting the bit GPLED in the board control register CTRLH REG.

The GP LED is not dedicated to any particular hardware or firmware function with exception of special power states of the LED PG as described above. Nevertheless, a red blinking GP LED is an indication that the BIOS code couldn't start.

While the CPU card is controlled by the BIOS firmware, the GP LED is used to signal board status information during POST (Power On Self Test). After successful operating system boot, the GP LED may be freely used by customer software. For details please refer to www.ekf.com/s/sc1/firmware/biosinfo.txt.

## HD (Hard Disk Activity) LED

The SC1-ALLEGRO offers a bicoloured LED marked as HD placed within the front panel. This LED, when blinking green, signals activity on any device attached to the SATA ports.

The red part of the HD LED isn't used currently.

As previously described, the green part of this LED may change its function dependent on the state of the LED PG.

## EB (Ethernet Backplane) LED

To monitor the link status and activity on both Ethernet ports attached to the backplane via the *CompactPCl*<sup>®</sup> Serial connector P6 a single bicoloured LED is provided in the front panel. The states are decoded as follows:

| 1_ETH   | 2_ETH   | LED EB       |

|---------|---------|--------------|

| no link | no link | OFF          |

| link    | no link | GREEN        |

| no link | link    | YELLOW       |

| link    | link    | GREEN/YELLOW |

Blinking of the LED EB in the appropriate colour means that there is activity on the port.

## Main Power Supply Control (PS ON#)

The SC1-ALLEGRO draws its power from the +12V main supply rail defined by the *CompactPCl*<sup>®</sup> Serial specification. The board has been designed to control this main power supply by use of the signal PS\_ON# (connector P1 pin E2). If the system enters the sleep state S5 (soft off), the signal PS\_ON# is pulled high, hence the main power supply is switched-off. The SC1-ALLEGRO is held in soft off state until a power management event (e.g. power button event triggered by the front panel handle) brings back the system to the S0 state.

In order to work as described above and to generate clean signals on PS\_ON#, the stand-by voltage +5VSTB is necessary. This optional power rail, tied to connector P1 pin B1, is also part of the CompactPCl® Serial specification. The stand-by power rail must be switched-on "always", independent of the state of PS\_ON#.

Nevertheless, +5VSTB is not mandatory to operate the SC1-ALLEGRO. If no stand-by power is available, the board creates this voltage from the main power rail. In this case it is important that the PS ON# signal is pulled down somewhere in the system.

## Power Supply Status (PWR FAIL#)

Power supply failures may be detected before the system crashes down by monitoring the signal PWR\_FAIL#. This active low line (connector P1 pin F3) is an addition to the *CompactPCl*® Serial specification and may be driven by the power supply. PWR\_FAIL# signals the possible failure of the main supply voltage +12V. On the SC1-ALLEGRO the signal PWR\_FAIL# is routed to GPIO6 of the QM77 PCH to analyse the state of the power supply unit.

## **Mezzanine Side Board Options**

The SC1-ALLEGRO is provided with several stacking connectors for attachment of a mezzanine expansion module (aka side board), suitable for a variety of readily available mezzanine cards (please refer to www.ekf.com/c/ccpu/mezz\_ovw.pdf for a more comprehensive overview). EKF furthermore offers custom specific development of side boads (please contact sales@ekf.de).

Most mezzanine expansion modules require an assembly height of 8HP in total, together with the CPU carrier board (resulting from two cards at 4HP pitch each).

In addition, cropped low profile mass storage mezzanine modules can be attached to J-HSE, which maintain the 4HP envelope, for extremely compact systems. Furthermore these small size modules may be combined with the full-size expansion boards (that means an assembly comprised of 3 PCBs).

| Related Documents Mezzanine Modules and Side Cards |                                                 |  |  |

|----------------------------------------------------|-------------------------------------------------|--|--|

| C4x Series Mezzanine Storage Modules               | www.ekf.com/c/ccpu/c4x_mezz_ovw.pdf             |  |  |

| Mezzanine Modules Overview                         | www.ekf.com/c/ccpu/mezz_ovw.pdf                 |  |  |

| The EKF Mezzanine Module Concept                   | www.ekf.com/c/ccpu/cpci_mezzanine_evolution.pdf |  |  |

| J-EXP               |                |  |  |

|---------------------|----------------|--|--|

| I/F Type            | Controller     |  |  |

| LPC (Low Pin Count) | CPU            |  |  |

| HD Audio            | CPU            |  |  |

| SMBus               | CPU (buffered) |  |  |

| 2 x USB 2.0         | PCH            |  |  |

| J-HSE        |            |  |  |  |

|--------------|------------|--|--|--|

| I/F Type     | Controller |  |  |  |

| SATA1        | PCH 3GT/s  |  |  |  |

| SATA2, SATA3 | PCH 6GT/s  |  |  |  |

| 4 x USB 2.0  | USB Hub    |  |  |  |

| J-PCIE       |            |  |  |  |

|--------------|------------|--|--|--|

| I/F Type     | Controller |  |  |  |

| PCI Express® | PE Switch  |  |  |  |

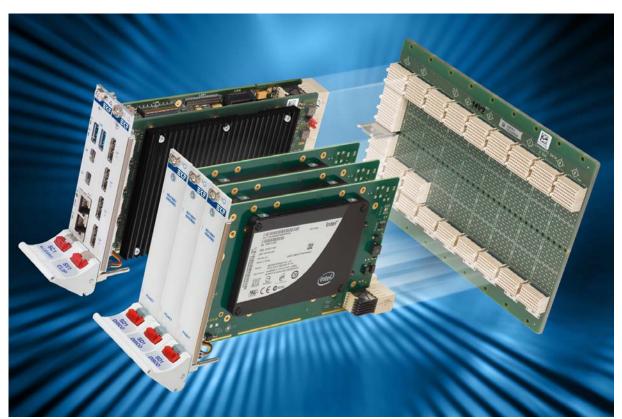

SC1-ALLEGRO with C42-SATA Low Profile Storage Module

4HP Front Panel Width with C42-SATA

SC1-ALLEGRO with C47-MSATA Low Profile Storage Module

4HP Front Panel Width with C47-MSATA

4HP Front Panel Width Assembly w. C48-M2

SC1-ALLEGRO with C48-M2 Dual M.2 SATA SSD Module

SC1-ALLEGRO with C44-SATA Assembly (8HP Front Panel)

SC1-ALLEGRO with C45-SATA Assembly (8HP Front Panel)

SC1-ALLEGRO with C43-SATA (Internal Connectors)

SC1-ALLEGRO with C41-CFAST Low Profile Storage Module

## CompactPCl® Serial

## **System Slot Controller**

The PICMG<sup>®</sup> CompactPCl<sup>®</sup> Serial specification defines a card slot system based on the modern high speed data-links PCI Express<sup>®</sup>, SATA, Ethernet and USB. The SC1-ALLEGRO, designed to act as a CompactPCl<sup>®</sup> Serial system slot controller, provides the resources of these interfaces. The backplane distributes them in the form of point to point connections to the peripheral slots.

The SC1-ALLEGRO allocates most but not all communication channels defined by *CompactPCl*<sup>®</sup> Serial on the backplane:

- ► Two PCle Links x8, 2.5GT/s, 5GT/s or 8GT/s (Fat Pipes)

- ► Four PCle Links x1, 2.5GT/s or 5GT/s

- Seven SATA Ports 3GT/s

- ► Two USB 3.0 Ports

- Six USB 2.0 Ports

- Two Gigabit Ethernet Ports

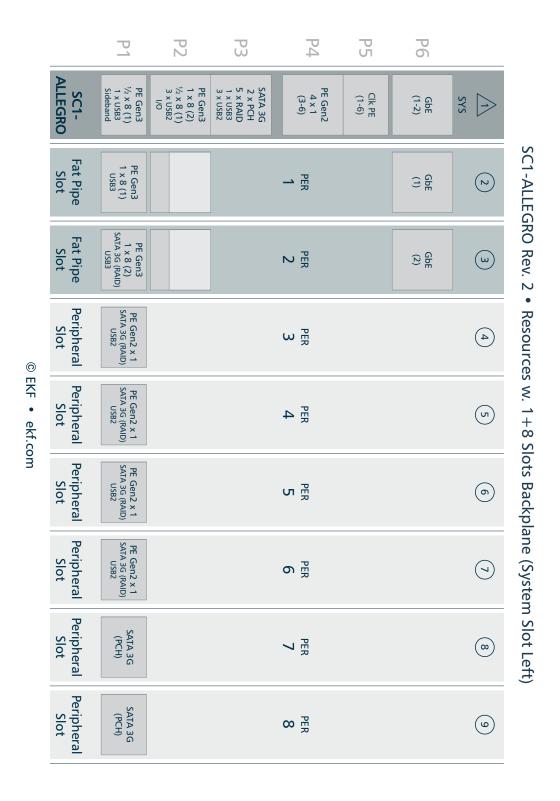

These resources maybe distributed on a typical 9-slot CompactPCl® Serial backplane as follows:

Note: The Assignment of the SATA Resources has changed with Revision 2 of the SC1-ALLEGRO. See sections "CompactPCI Serial Backplane Connector P3" for details.

© EKF -36-

SC1-ALLEGRO on a Backplane w. System Slot Left Aligned

Backplane w. System Slot Right Aligned

SC1-ALLEGRO Rev. 2 • Resources w. 1+8 Slots Backplane (System Slot Right)

|                    | P                                     | P2                                                    | P3                                                     | P4                        | P5              | P6           |       |

|--------------------|---------------------------------------|-------------------------------------------------------|--------------------------------------------------------|---------------------------|-----------------|--------------|-------|

| Peripheral<br>Slot | SATA 3G<br>(PCH)                      |                                                       |                                                        | PER                       |                 |              |       |

| Peripheral<br>Slot | SATA 3G<br>(PCH)                      |                                                       |                                                        | PER<br>7                  |                 |              | 2     |

| Peripheral<br>Slot | PE Gen2 x 1<br>SATA 3G (RAID)<br>USB2 |                                                       |                                                        | PER<br>6                  |                 |              | (B)   |

| Peripheral<br>Slot | PE Gen2 x 1<br>SATA 3G (RAID)<br>USB2 |                                                       |                                                        | PER<br>5                  |                 |              | 4     |

| Peripheral<br>Slot | PE Gen2 x 1<br>SATA 3G (RAID)<br>USB2 |                                                       |                                                        | PER<br>4                  |                 |              | 5     |

| Peripheral<br>Slot | PE Gen2 x 1<br>SATA 3G (RAID)<br>USB2 |                                                       |                                                        | <b>P</b> ER               |                 |              | 6     |

| Fat Pipe<br>Slot   | PE Gen3 1 x 8 (2) SATA 3G (RAID) USB3 |                                                       |                                                        | PER<br>2                  |                 | GbE<br>(2)   | 7     |

| Fat Pipe<br>Slot   | PE Gen3<br>1 x 8 (1)<br>USB3          |                                                       |                                                        | PER                       |                 | GbE<br>(1)   | 8     |

| SC1-<br>ALLEGRO    | PE Gen3 1/2 x 8 (1) 1 x USB3 Sideband | PE Gen3<br>1 x 8 (2)<br>1½ x 8 (1)<br>3 x USB2<br>1/0 | SATA 3G<br>2 x PCH<br>5 x RAID<br>1 x USB3<br>3 x USB2 | PE Gen2<br>4 × 1<br>(3-6) | Clk PE<br>(1-6) | GbE<br>(1-2) | SYS 9 |

© EKF • ekf.com

## **Peripheral Slot Operation**

Beyond that the SC1-ALLEGRO is operable in periphery slots as well. In this case it acts as a satellite system, linked to other (processor-) boards by its backplane Ethernet connections. The other resources associated with the backplane like PCI Express, SATA or USB are not usable in this situation.

Some of the following, system slot dedicated control signals get an altered function or will be disconnected from the backplane:

- ► PWRBTN# (Connector P1 Pin C3) will be disconnected

- PWR FAIL# (Connector P1 Pin F3) becomes GA1

- ▶ PRST# (Connector P1 Pin H2) becomes RST# and will be disconnected

- ► WAKE# (Connector P1 Pin I2) will be disconnected

- ► SGPIO (Connector P1 Pins G3/H3/J3/K3) will be disconnected

One result of that is, that a SC1-ALLEGRO plugged into a peripheral slot will not get a reset even if the system controller forces the reset signal on the backplane to an active state.

## **Board Hot-Plug**

Hot-plug of the SC1-ALLEGRO is not supported, no matter whether it is working as a system controller or satellite board.

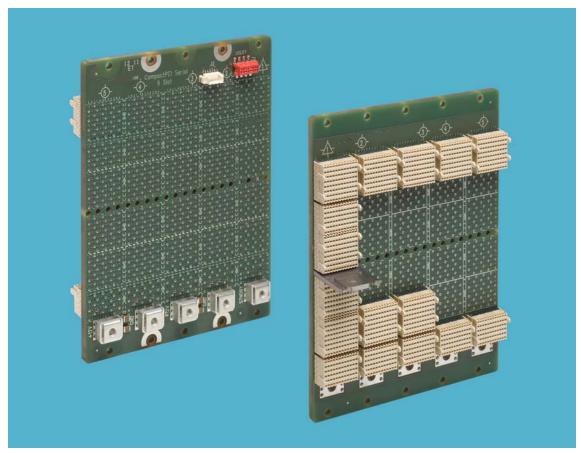

SC1-ALLEGRO as System Slot Controller for CompactPCI® Serial Systems

CompactPCI® Serial Rack

BluBoxx Series Small Systems Rack

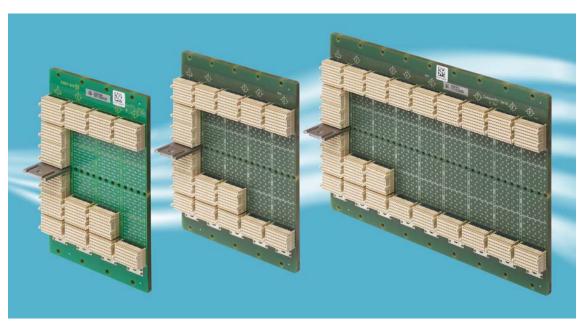

CompactPCI® Serial Backplanes

1+4 Slots CompactPCI® Serial Backplane

## **Installing and Replacing Components**

#### Before You Begin

## Warnings

The procedures in this chapter assume familiarity with the general terminology associated with industrial electronics and with safety practices and regulatory compliance required for using and modifying electronic equipment. Disconnect any telecommunication links, networks or procedures described in this chapter. Failure links before you open the system or perform or equipment damage. Some parts of the the power switch is in its off state.

the system from its power source and from modems before performing any of the to disconnect power, or telecommunication any procedures can result in personal injury system can continue to operate even though

#### Caution

Electrostatic discharge (ESD) can damage components. Perform the procedures described in this chapter only at an ESD workstation. If such a station is not available, you can provide some ESD protection by wearing an antistatic wrist strap and attaching it to a front panel. Store the board only in its metal part of the system chassis or board original ESD protected packaging. Retain the original packaging (antistatic bag and antistatic box) in case of returning the board to EKF for repair.

## Installing the Board

## Warning

This procedure should be done only by qualified technical personnel. Disconnect the system from its power source before doing the procedures described here. Failure to disconnect power, or telecommunication links before you open the system or perform any procedures can result in personal injury or equipment damage.

Typically you will perform the following steps:

- Switch off the system, remove the AC power cord

- Attach your antistatic wrist strap to a metallic part of the system

- Remove the board packaging, be sure to touch the board only at the front panel

- Identify the related *CompactPCl*® slot (peripheral slot for I/O boards, system slot for CPU boards, with the system slot typically most right or most left to the backplane)

- Insert card carefully (be sure not to damage components mounted on the bottom side of the board by scratching neighboured front panels)

- A card with onboard connectors requires attachment of associated cabling now

- Lock the ejector lever, fix screws at the front panel (top/bottom)

- Retain original packaging in case of return

## Removing the Board

## Warning

This procedure should be done only by qualified technical personnel. Disconnect the system from its power source before doing the procedures described here. Failure to disconnect power, or telecommunication links before you open the system or perform any procedures can result in personal injury or equipment damage.

Typically you will perform the following steps:

- Switch off the system, remove the AC power cord

- Attach your antistatic wrist strap to a metallic part of the system

- Identify the board, be sure to touch the board only at the front panel

- Unfasten both front panel screws (top/bottom), unlock the ejector lever

- Remove any onboard cabling assembly

- Activate the ejector lever

- Remove the card carefully (be sure not to damage components mounted on the bottom side of the board by scratching neighboured front panels)

- Store board in the original packaging, do not touch any components, hold the board at the front panel only

## Warning

Do not expose the card to fire. Battery cells and other components could explode and cause personal injury.

#### **EMC Recommendations**

In order to comply with the CE regulations for EMC, it is mandatory to observe the following rules:

- The chassis or rack including other boards in use must comply entirely with CE

- Close all board slots not in use with a blind front panel

- Front panels must be fastened by built-in screws

- Cover any unused front panel mounted connector with a shielding cap

- External communications cable assemblies must be shielded (shield connected only at one end of the cable)

- Use ferrite beads for cabling wherever appropriate

- Some connectors may require additional isolating parts

## **Recommended Accessories**

| Blind CPCI Front<br>Panels | EKF Elektronik                       | Widths currently available (1HP=5.08mm): with handle 4HP/8HP without handle 2HP/4HP/8HP/10HP/12HP                    |

|----------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Ferrit Bead Filters        | ARP Datacom,<br>63115 Dietzenbach    | Ordering No.<br>102 820 (cable diameter 6.5mm)<br>102 821 (cable diameter 10.0mm)<br>102 822 (cable diameter 13.0mm) |

| Metal Shielding<br>Caps    | Conec-Polytronic,<br>59557 Lippstadt | Ordering No. CDFA 09 165 X 13129 X (DB9) CDSFA 15 165 X 12979 X (DB15) CDSFA 25 165 X 12989 X (DB25)                 |

## Replacement of the Battery

When your system is turned off, a battery maintains the voltage to run the time-of-day clock and to keep the values in the CMOS RAM. The battery should last during the lifetime of the SC1-ALLEGRO. For replacement, the old battery must be desoldered, and the new one soldered. We suggest that you send back the board to EKF for battery replacement.

## Warning

Danger of explosion if the battery is incorrectly replaced or shorted. Replace only with the same or equivalent type. Do not expose a battery to fire.

## **Technical Reference**

## **Local PCI Devices**

The following table shows the on-board PCI devices and their location within the PCI configuration space. Several devices are part of the processor and platform controller hub QM77.

| Bus #           | Device # | Function # | Vendor ID | Device ID                            | Description                                                                                                                   |

|-----------------|----------|------------|-----------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 0               | 0        | 0          | 0x8086    | 0x0154                               | Processor Host Bridge/DRAM Controller                                                                                         |

| 0               | 1        | 0          | 0x8086    | 0x0151                               | Processor PCI Express Controller                                                                                              |

| 0               | 2        | 0          | 0x8086    | 0x0156                               | Processor Integrated Graphics Device                                                                                          |

| 0               | 6        | 0          | 0x8086    | 0x015D                               | Processor PCI Express Controller                                                                                              |

| 0               | 20       | 0          | 0x8086    | 0x1E31                               | USB xHCl Controller                                                                                                           |

| 0               | 22       | 0          | 0x8086    | 0x1E3A                               | Intel ME Interface #1                                                                                                         |

| 0               | 22       | 1          | 0x8086    | 0x1E3B                               | Intel ME Interface #2                                                                                                         |

| 0               | 22       | 2          | 0x8086    | 0x1E3C                               | Intel ME IDE Redirection                                                                                                      |

| 0               | 22       | 3          | 0x8086    | 0x1E3D                               | Intel ME Keyboard Text Redirection                                                                                            |

| 0               | 25       | 0          | 0x8086    | 0x1502                               | PCH Gigabit LAN NC1 (82579LM)                                                                                                 |

| 0               | 26       | 0          | 0x8086    | 0x1E2D                               | USB EHCI Controller #2                                                                                                        |

| 0               | 27       | 0          | 0x8086    | 0x1E20                               | Intel High Definition Audio Controller                                                                                        |

| 0               | 28       | 0-7        | 0x8086    | 0x2448                               | PCH PCI Express Port 1-8                                                                                                      |

| 0               | 29       | 0          | 0x8086    | 0x1E26                               | USB EHCI Controller #1                                                                                                        |

| 0               | 31       | 0          | 0x8086    | 0x1E55                               | LPC Bridge                                                                                                                    |

| 0               | 31       | 2          | 0x8086    | 0x1E01<br>0x1E03<br>0x282A<br>0x1E07 | SATA: Non-AHCI/RAID (Ports 0-3) 1) SATA: AHCI Mode 1) SATA: Intel Rapid Storage Tech. RAID Mode 1) SATA: RAID Mode Capable 1) |

| 0               | 31       | 3          | 0x8086    | 0x1E22                               | SMBus Controller                                                                                                              |